Software Tools

FPGA and FPSoC integrated development environment self-developed by Anlogic Infotech

TangDynasty? (TD)

TangDynasty? (TD) is an FPGA integrated development environment independently developed by Anlogic Infotech. In addition to offering an excellent third-party design verification tool interface to strongly support the design of all applications based on Anlogic Infotech FPGA products, it supports industry-standard design inputs, involving a complete circuit optimization flow and rich analysis and debugging tools.

-

RTL synthesis

-

Gate level synthesis

-

Layout optimization

-

Bitstream generation

-

Cabling optimization

-

Product Overview

-

Product Features

Product Overview

TangDynasty? (TD) software is an Anlogic Infotech self-developed FPGA integrated development environment completely based on users' needs: simple interface, intelligent behavior, efficient operation, and support for Windows and Linux operating system. Innovative software algorithms effectively support ELF, EAGLE, SF1 and other series of devices of different scales; expandable software architecture quickly supports multiple product types including single-chip, SIP, SOC; and structured software development platform supports accurate simulation and rapid evaluation of new hardware structures, user design IP protection and bitstream encryption confidentiality.

Product Features

-

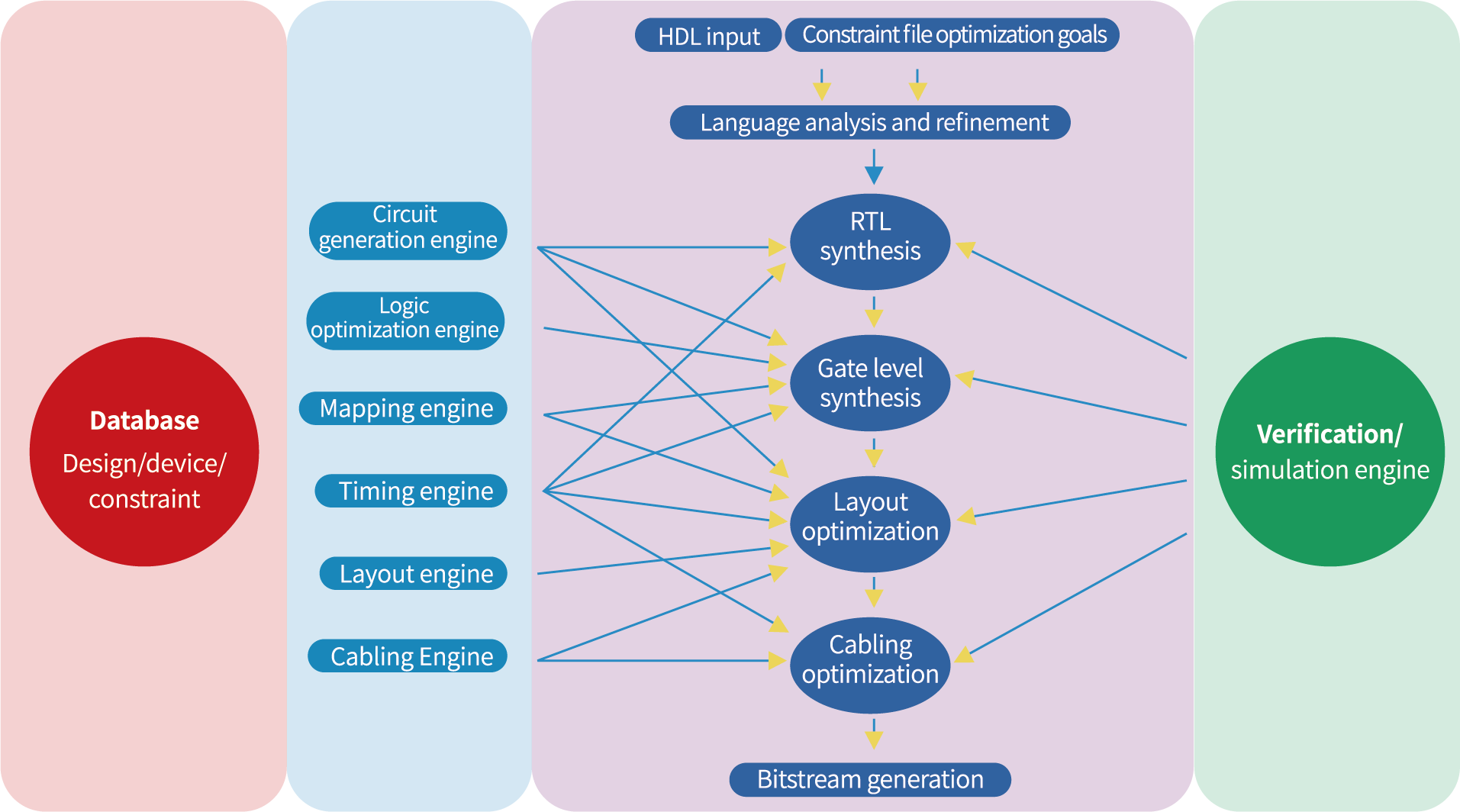

Software architecture

Software architectureArchitecture-optimized algorithm engine, improving the efficiency of RTL input, synthesis, layout, and cabling

-

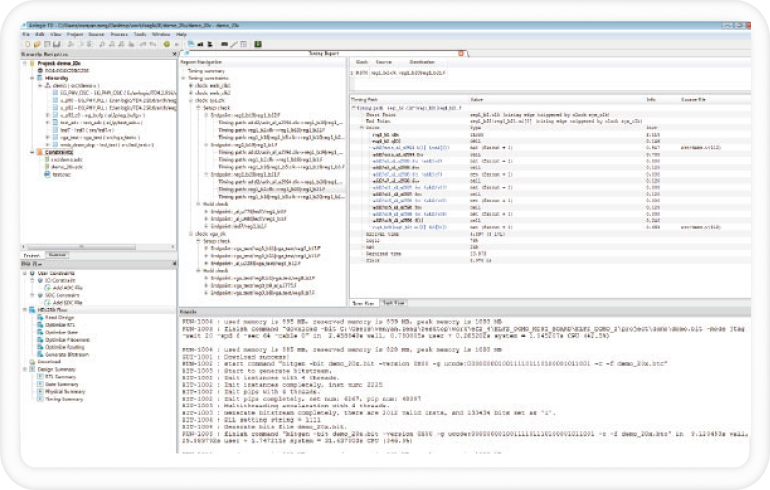

Software Interface

Software InterfaceSimple interface, intelligent behavior, efficient operation

-

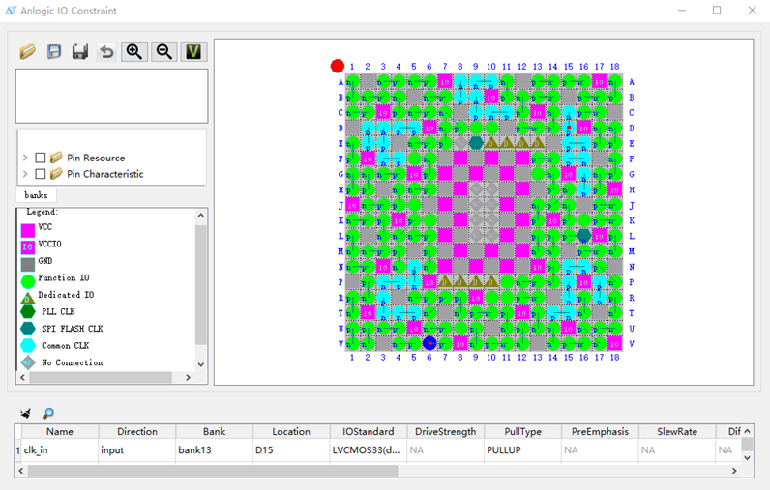

Position Constraint Tool

Position Constraint ToolGraphical operation for customer convenience

-

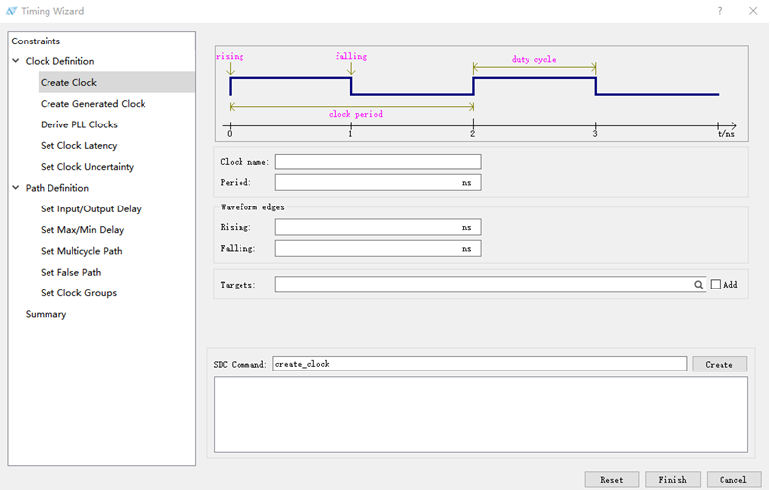

Timing Constraint Tool

Timing Constraint ToolSupport multiple timing constraints to improve system performance